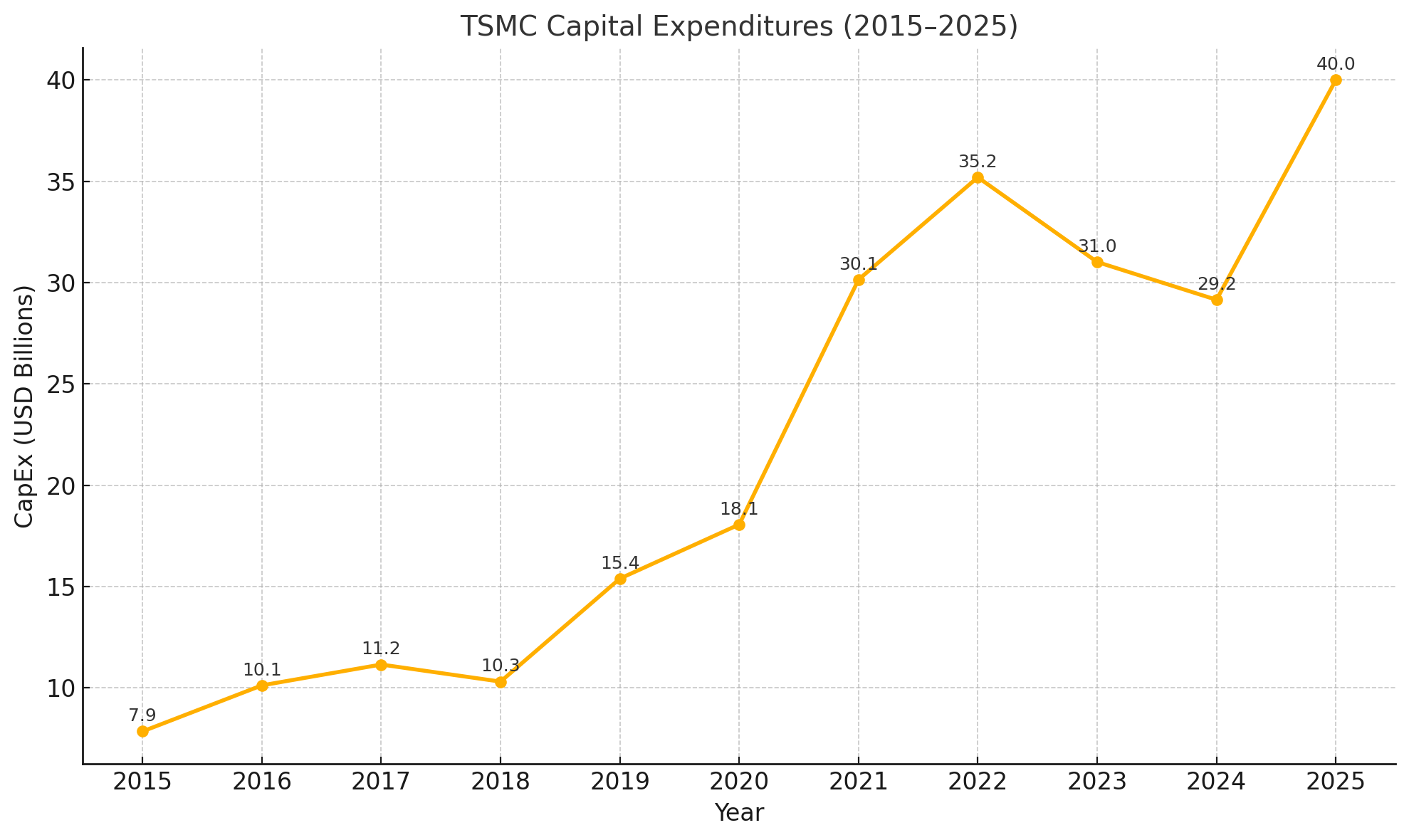

TSMC's share of the chipmaking market has been increasing, and so has the company's capital expenditure (CapEx), which has increased fivefold since 2015. The company plans to spend between $38 billion and $42 billion on capacity expansion in 2025, with the hopes of building eight semiconductor fabrication facilities and one advanced packaging facility in 2025.

"From 2017 to 2020, every year we built on average three fabs per year," said Dr. Cliff Hou, SVP and Deputy Co-COO at TSMC, at the most recent 2025 North America Technology Symposium. "From 2021 to 2024, we increased to five fabs per year. This year, we will increase to nine new fabs per year to support our strong growth and your business. Among those nine fabs, eight are wafer fabs and one is an advanced packaging facility."

Swipe to scroll horizontally

Site Name | Phase | Capabilities | Fab Location | Status |

AP7 | 1 | Advanced packaging | Chiayi, Taiwan | In construction as of September 2024 |

Fab 20 | 1 | A16, N2 | Hsinchu, Taiwan | Equipping/Ramping in H2 2025 |

Fab 21 | 2 | N3 | Phoenix, Arizona | Equipping |

Fab 21 | 3 | A16, N2 | Phoenix, Arizona | In construction as of April 2025 |

Fab 22 | 1 | A16, N2 | Kaohsiung, Taiwan | Equipping/Ramping in H2 2025 |

Fab 23 - JASM | 2 | Sub-10nm | Kumamoto, Japan | In construction as of January 2025 |

Fab 24 - ESMC | 1 | N12, N16, N22, N28 | Dresden, Germany | In construction as of August 2024 |

Fab 25 | 1 | A14 (?) | Taichung, Taiwan | To be constructed in late 2025 |

TSMC's new capacity plans are huge. Later this year, it plans to start ramping production of chips using its N2 (2nm-class) process technology at Fab 20 and Fab 22 in Taiwan. The same production facilities will be used to build chips on TSMC's N2P and A16 (1.6nm-class) process technologies, starting in late 2026.

The company is ramping up its Fab 21 phase 1 in Arizona and is about to begin equipping its N3-capable Fab 21 phase 2, as construction has concluded. TSMC also began building the A16/N2-capable Fab 21 phase 3 in April 2025.

In addition, the company is building its Fab 23 phase 2 in Japan and Fab 24 phase 1 in Germany.

Finally, TSMC is set to begin construction of its Fab 25 in Taichung, Taiwan. This fab — set to come online in 2028 — will be used for post A16/N2 process technologies. So, it's likely that it will be one of the facilities which will produce chips on the A14 (1.4nm-class) production node, and more advanced processes.

Truth to be told, TSMC's way of counting new production facilities is a bit convoluted. The company is counting all facilities that are, or will be, in the pipeline this calendar year. It also disregards whether the fab's construction is set to start, has just started, or if the fab is about to start ramping. By TSMC's count, they are all "new" facilities. Even when using this method, we could only count seven new fabs and one advanced packaging facility. However, Tom's Hardware has reached out to TSMC to clarify this.

In total, TSMC is either building or equipping eight or nine new production facilities in 2025. This is the highest number of new production facilities being constructed or equipped simultaneously in the company's history.

The company's capital spend in 2025 will be between $38 billion and $42 billion. This is up from $29.2 billion in 2024, and much higher than the previous record, which was $35.2 billion in 2022.

Such a huge spend is not only a result of TSMC building more fabs than usual to meet demand, but also a result of fabs getting more expensive.

On the demand for TSMC's chips, many of its existing customers are increasing orders because its AI processors are getting physically bigger than its usual products. Therefore, they need to process more wafers.

The same logic also applies to fab costs, which are also getting higher. This is due to TSMC is expanding its usage of EUV lithography, and other sophisticated manufacturing methods. Each Low-NA EUV system from ASML is priced around $235 million, depending on configuration, and TSMC needs more of them every year.

Another factor in TSMC's rising fab costs will also include its increased adoption of Low-NA EUV machines. But, at some point, it will also start using ASML's upcoming High-NA EUV tools, which are expected to cost $380 million per unit.

When you combine all of these factors, TSMC's aggressive CapEx of up to $42 billion in 2025 starts to make some sense. However, as to whether or not all of these plans are completed on-time, and to schedule remains a determining factor in the chip manufacturer's continued success.

Follow Tom's Hardware on Google News to get our up-to-date news, analysis, and reviews in your feeds. Make sure to click the Follow button.

6 months ago

90

6 months ago

90

English (US) ·

English (US) ·