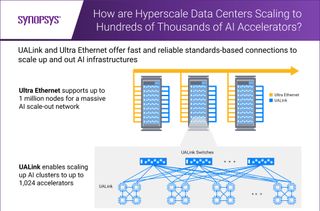

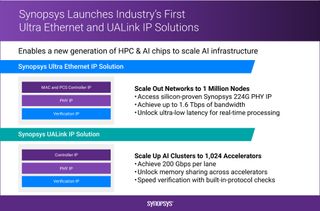

Synopsys on Wednesday announced the availability of its silicon-proven Ultra Ethernet IP solution for next-generation AI clusters with up to one million nodes, plus a UALink IP solution for linking massive pods with up to 1,024 accelerators. The IPs can be used to develop next-generation Ultra Ethernet network controllers, network interface cards, switches, UALink fabrics, and other connectivity solutions.

Synopsys Ultra Ethernet IP stack includes MAC and PCS controller, the silicon-proven Synopsys 224G PHY, and verification IP compliant with the UEC specification and adhering to the latest IEEE 802.3 and OIF-224G standards. The IP supports a wide range of data rates, including 4 x 400G, 2 x 800G, and 1.6T Ethernet, using high-speed 112 Gbps and 224 Gbps SerDes. Also, the IPs support all the key features that Ultra Ethernet has to support, including advanced error correction mechanisms, low latency, up to one million nodes, and intelligent multipathing, which dynamically distributes data packets across optimal routes.

Many of Synopsys's UE IPs are already supported, so by using them chip and device designers can save time, reduce risk, and speed up their time to market. In general, Synopsys has a full silicon implementation for network cards, switches, AI accelerators, smart NICs, and many others.

"Juniper has already introduced the industry's first 800GbE capability with its PTX10002-36QDD Packet Transport Router, which utilizes our proprietary Express 5 ASIC with Synopsys Ethernet IP," said Debashis Basu, senior vice president of Juniper Engineering. "We will continue to partner with Synopsys and leverage the latest technologies from the Ultra Ethernet Consortium (UEC) to transition into the 1.6TbE era. This indicates our ongoing innovation in high-speed networking to achieve our goal to significantly improve scale, reliability, and performance in data center networks. This is particularly important as AI workloads continue to grow exponentially, making such networks much more efficient and cost-effective."

In addition to Ultra Ethernet IP stack, Synopsys also has UALink IP solution consisting of PHY, controller, and verification IP to enable high-speed scale-up connections for AI accelerators akin to NVLink used by Nvidia. The UALink technology facilitates the connection of up to 1,024 accelerators per pod at 200 Gbps. Just like Ultra Ethernet, UALink IP incorporates features that reduce delays and enhance the overall performance of AI systems. The key capability of UALink is support for shared memory access between processors using RDMA aimed to eliminate performance bottlenecks that commonly occur in AI clusters.

Synopsys plans to roll out availability of its new connectivity technologies in two phases. The Ultra Ethernet IP stack is expected to launch in the first half of 2025. Following that, the UALink IP solution, with its controller, PHY, and verification IP, is slated for release in the latter half of 2025.

1 week ago

2

1 week ago

2

English (US) ·

English (US) ·