Intel disclosed several chip packaging breakthroughs at the Electronic Components Technology Conference (ECTC), outlining the technical merits of multiple new chip packaging techniques. We spoke with Dr. Rahul Manepalli, an Intel Fellow and VP of Substrate Packaging Development, for more details on three of the new packaging technologies: EMIB-T for boosting both the size of chip packages and power delivery capabilities to support new technologies like HBM4/4e, a new disagregated heat spreader design, and a new thermal bonding technique that improves reliability, yields, and enables scaling to finer chip-to-chip connections. Intel also participated in 17 other new papers presented at the event.

Intel Foundry aims to produce chips for both Intel's own internal use and for external companies, utilizing leading-edge process node technology. However, modern processors are increasingly deployed with complex, heterogeneous designs that integrate multiple types of computing and memory components into a single chip package, thereby amplifying performance, cost, and power efficiency gains. These chip designs rely upon increasingly complex advanced packaging techniques that serve as the bedrock of heterogeneous designs, so continued evolution is critical as Intel keeps pace with competitors like TSMC.

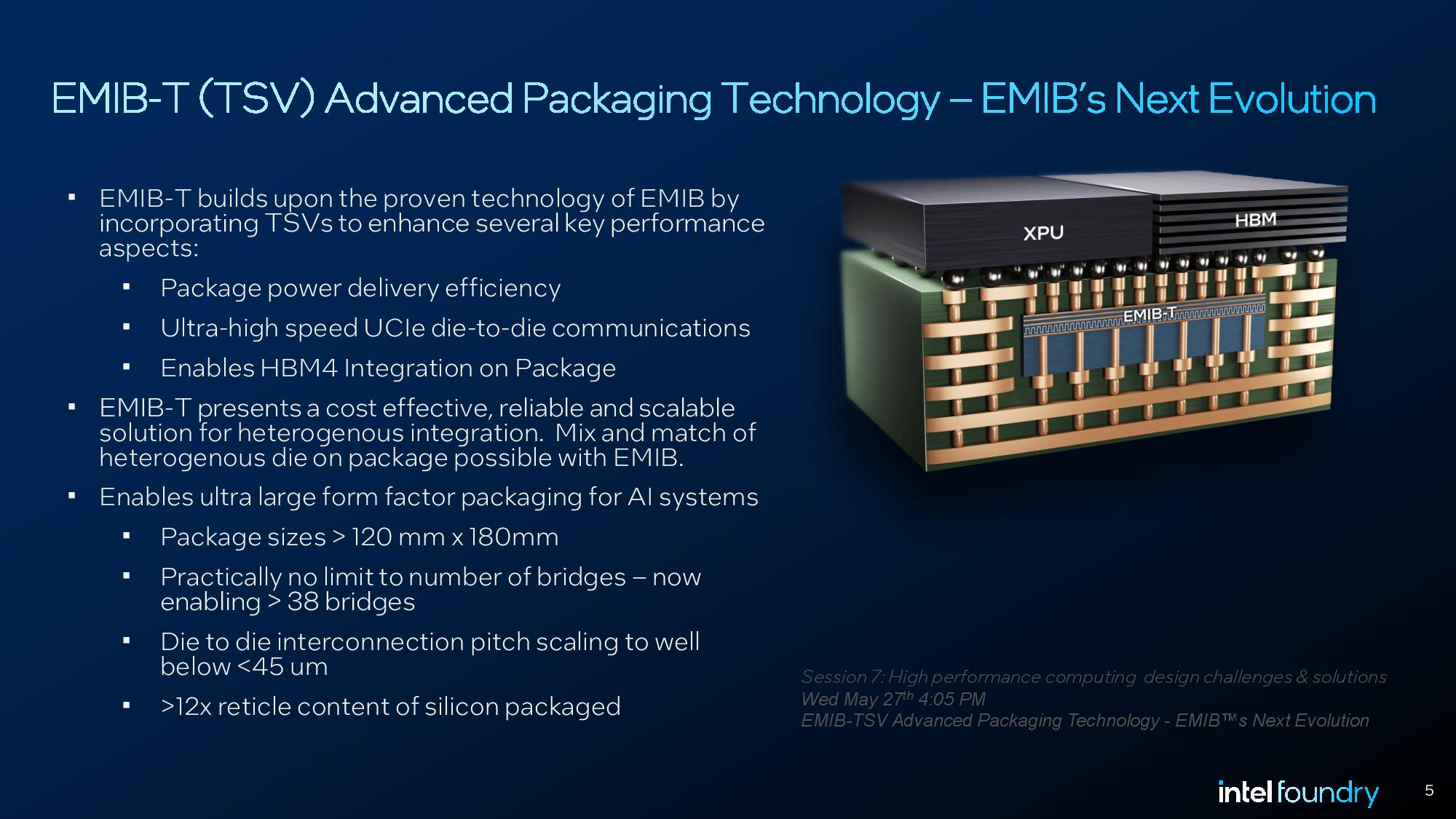

Intel's new EMIB-T, originally disclosed at its Intel Direct Connect event last month, incorporates through-silicon vias (TSVs) into its already widely used EMIB technology —a silicon bridge embedded in a package substrate that provides communication and power plumbing between chiplets/dies.

This next evolution of EMIB enhances critical package power delivery efficiency metrics and speeds die-to-die communication. EMIB-T can be used to more effectively power compute and memory components — whereas standard EMIB connections struggled with high voltage droop due to a cantilevered power delivery path, EMIB-T utilizes TSVs to provide power delivery from the bottom of the chip package via TSV bridge dies, thus enabling a direct, low-resistance path for power delivery that's critical for HBM4/4e integration.

Naturally, the use of TSVs also boosts die-to-die communication bandwidth, enabling the integration of high-speed HBM4/4e memory packages and the use of the UCIe-A interconnect to increase data transfer rates to 32 Gb/s or higher. Routing power and signals through the same interface introduces 'noise' in the signal path, but Intel integrated high-powered MIM capacitors into the bridge to help ensure consistent communication signaling.

EMIB-T also enables much larger chip package sizes, reaching 120x180mm, and supports more than 38 bridges and more than 12 recticle-sized die in a single large chip package. Additionally, the first generation of EMIB enabled a 55-micron bump pitch, a critical interconnect density metric, while the second-generation EMIB scaled down to a 45-micron pitch. Intel's paper demonstrates an EMIB-T design with a 45-micron pitch, but notes that the new technology supports "well below" 45-micron pitches, saying it will go to 35-micron pitches soon and has 25-micron pitches in development. Intel hasn't shared the picojoules-per-bit (pJ/bit) power efficiency metrics. EMIB-T is also compatible with either organic or glass substrates, with the latter being a key strategic direction for Intel's future chip packaging endeavors.

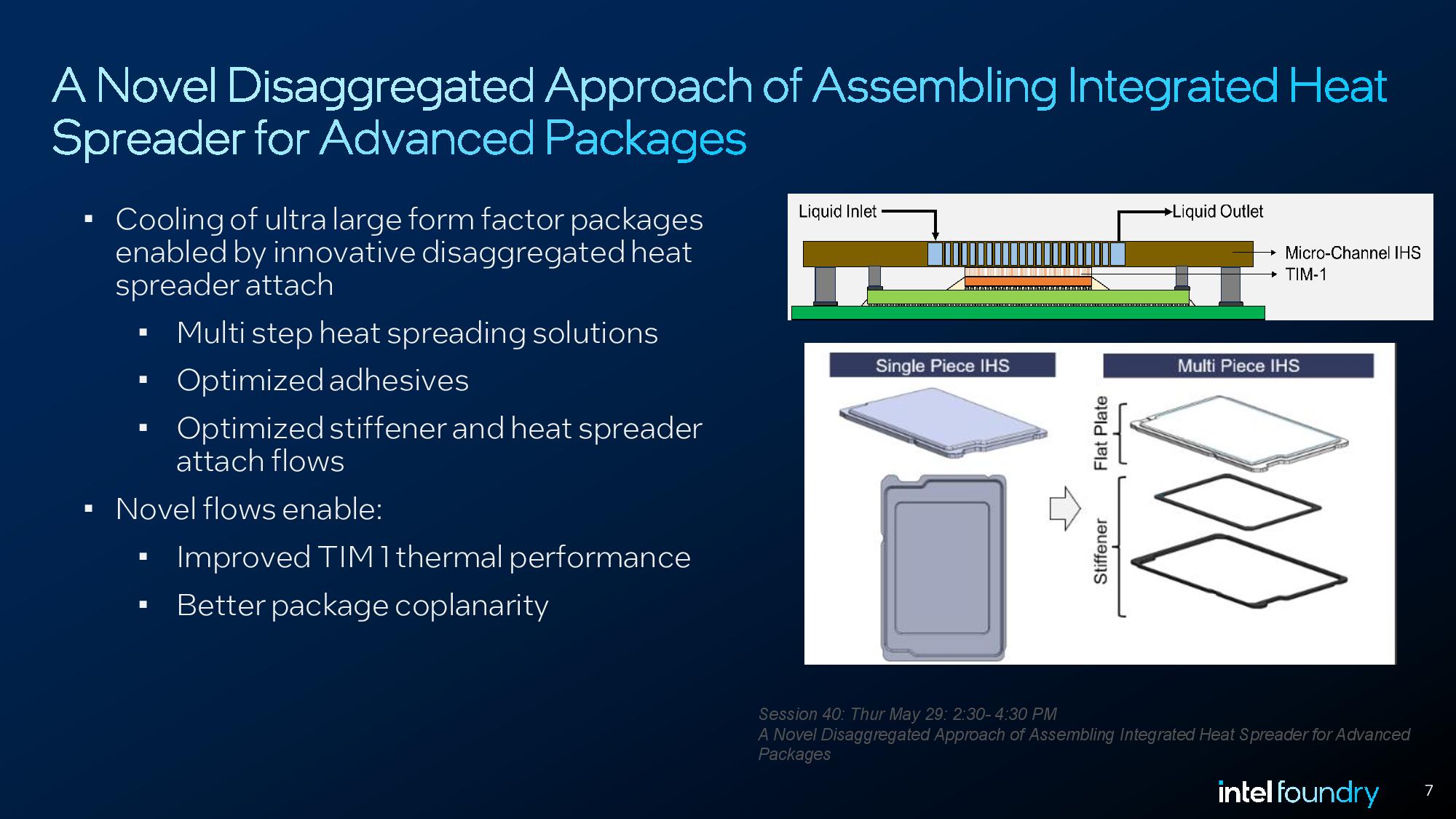

The AI revolution is pushing chip package sizes to new frontiers, and with that comes increased power consumption that introduces vexing cooling challenges. Intel also disclosed a new disaggregated heat spreader technique that breaks the heat spreader into a flat plate and a stiffener to improve coupling between the heat spreader and the thermal interface material (TIM) that resides between the heat spreader and the underlying die. Among other benefits, this technique helps reduce voids in solder TIM coupling by 25%.

Intel's illustration shows a heatspreader with integrated micro-channels that carry liquid directly through the IHS to cool the processor, much like we saw on display at its Direct Connect event. While the paper focused on the effects of breaking the heatspreader into multiple pieces, the inclusion of this tech, which can cool processor packages with a TDP up to 1000W, highlights that Intel is approaching the chip cooling problem from multiple angles.

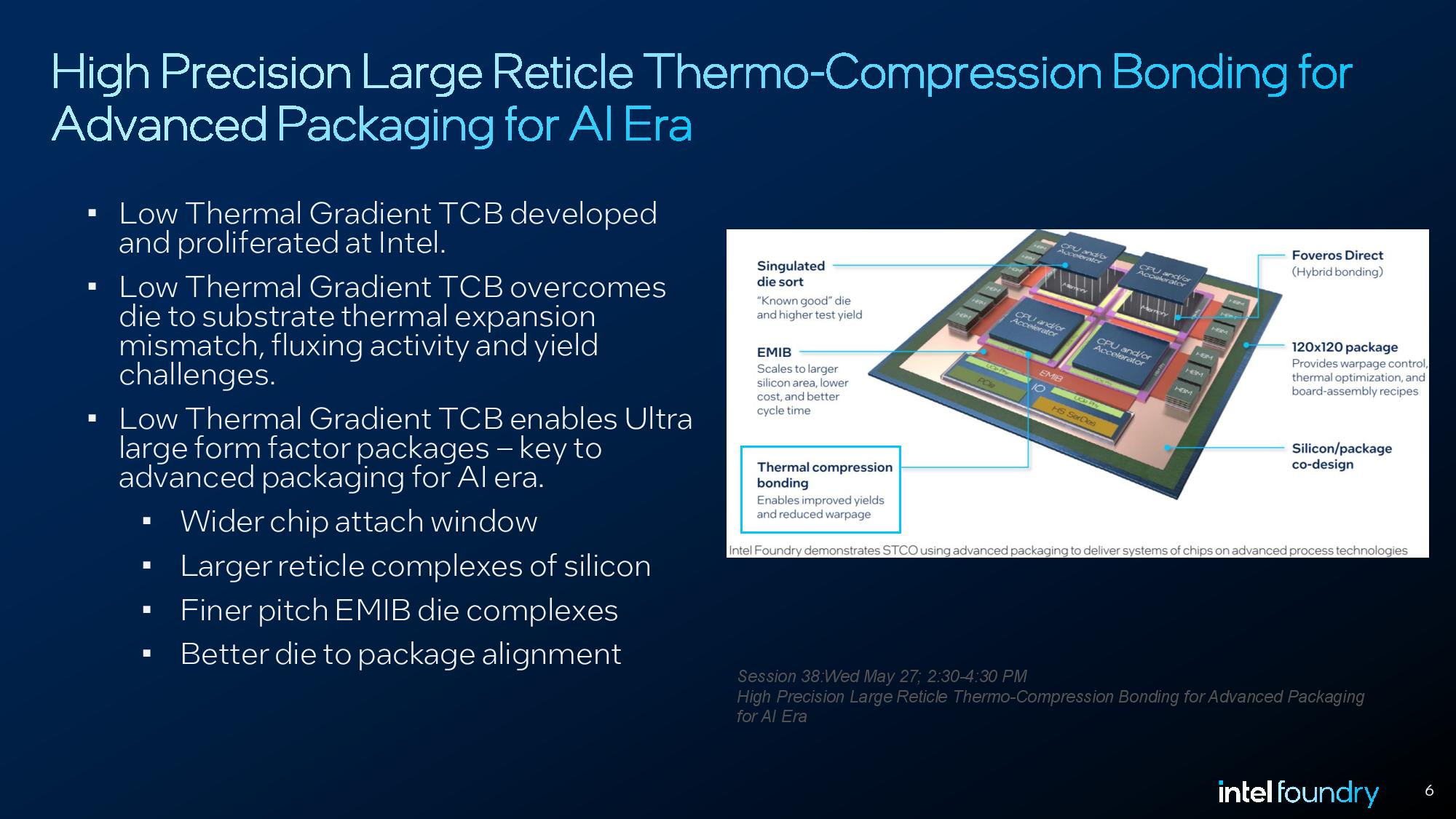

Intel has utilized thermal compression bonding techniques in both its server and consumer products; however, it has now developed a new thermal compression bonding process specifically for large package substrates that helps overcome die and substrate warpage during the bonding process.

This new technique minimizes the thermal delta between the package substrate and the die during the bonding process, thereby improving yield and reliability metrics and enabling much larger chip packages than are currently possible in high volume manufacturing. It also enables finer pitches for EMIB connections, helping to squeeze out more density from EMIB-T technology.

Having a well-rounded and competitive suite of packaging technologies is crucial for Intel Foundry as it aims to provide its customers with the most comprehensive range of chip production options possible. Advanced chip packaging techniques enable customers to integrate different types of chips, such as CPUs, GPUs, and memory, from multiple vendors into a single package, thereby reducing the risk of transitioning entirely to Intel's process nodes for all componentry. In fact, Intel also offers packaging services for chips that don't use any Intel-fabbed components at all, helping to build relationships with potential new customers for its chip-fabbing services.

Chip packaging has also emerged as one of the leading services for Intel's external customers, which currently include industry heavyweights such as AWS and Cisco, among others, as well as the US government's RAMP-C and SHIP projects. These packaging contracts serve as the fastest on-ramp for Intel Foundry revenue generation, as producing chips with leading-edge process nodes requires significantly longer lead times.

6 months ago

107

6 months ago

107

English (US) ·

English (US) ·